**JESRT**

## ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

## COMPARATIVE CONTROL OF DVR FOR POWER QUALITY IMPROVEMENT UNDER UNBALANCED VOLTAGE SAG

H. Mallesam Dora<sup>\*1</sup> & M Vikas<sup>2</sup>

<sup>\*1</sup>Assoc. Professor, Avanthi's Research Technological Academy, India <sup>2</sup>M. Tech student, Avanthi's Research Technological Academy, India

### **DOI**: 10.5281/zenodo.1284202

#### ABSTRACT

A Power quality problem is an occurrence manifested as a nonstandard voltage, current or frequency that results in a failure or a disoperation of end user equipments. Power quality is certainly a major concern in the present era; it becomes especially important with the introduction of sophisticated devices, whose performance is very sensitive to the quality of power supply. Voltage sag is one of the severe power quality problems. This report addresses all the different aspects related to voltage sag problem, such as: its types, consequences and mitigation. At present, a wide range of very flexible controllers, which capitalize on newly available power electronics components, are emerging for custom power applications. Among these, the distribution static compensator (D-STATCOM) and the dynamic voltage restorer (DVR) are most effective devices, both of them based on the VSC principle. MATLAB SIMULINK has been used in this project to perform the modeling and analysis of such controllers. A DVR injects a voltage in series with the system voltage to correct the voltage sag. The steady state performance of DVR is obtained for various voltage sags/swell levels. Comprehensive results are presented to assess the performance of each device as a potential custom power solution.

Keywords: Power Quality, DSTATCOM, DVR, Voltage Sag, Voltage Swell.

### I. INTRODUCTION

Power quality (PQ) problems in the distribution system and their solutions have received much attention in the recent years. The incorporation of the large numbers of nonlinear loads for improved efficiency and their better controlled use, the nonconventional power production technologies such as solar and wind power, and the various power electronics devices used in the system introduce new problems, like additional harmonic voltage/current distortion, particularly higher order harmonics [1]-[5]. Under the generic name of custom power devices [2], a new group of devices is developed and used for improving the PQ in the distribution system. As per the standard such as the IEEE 519 [6], a number of custom power devices are installed and used at the consumer premises to protect the critical loads. The dynamic voltage restorer (DVR), one of the aforementioned devices, is used for improving the PQ of the load terminal voltages against voltage sags, swells, transients, and harmonic distortions in the source voltages. A DVR is a voltage-source converter (VSC)-based power electronics device connected in series between the supply and the critical loads, which are to be protected from the supply side voltage quality problems, other than outages, by injecting the required compensating voltage through DVR into the distribution line. A DVR can restore a balanced sinusoidal load voltage of desired amplitude even when the source voltage is unbalanced and/or distorted. The voltage injected by self supported DVR is in quadrature with the feeder current; hence, it does not need any active power during steady state. However, its disadvantage is that, in case of the voltage sag/swell, the restored voltage may not be in phase with the pre-sag/pre-swell voltage. The self-supported DVR is used when the phase jump, caused by the quadrature voltage injection, is affordable. The DVR is an important controller in the custom power parkm [7]. The analysis, design, and voltage injection schemes of the self-supported DVR are discussed in [2], [10], and [11], and the different control strategies for the DVR have been developed in [8]-[17]. Control techniques based on synchronous reference frame (SRF) theory (SRFT) [8], Adeline-based fundamental extraction [9], instantaneous symmetrical component theory [10], [11], energy optimized control [12], POR instantaneous power theory [13], symmetrical component estimation [14], etc., for the DVR are reported in the literature. Different topologies of the DVR are discussed in [19]. The DVR supported by a capacitor has become popular as a cost effective solution for the protection of sensitive loads from the supply-side voltage quality problems. Currently, most of

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

the research is on DVR dealing with the protection of balanced linear load; however, there are a few which are related to the protection of unbalanced and nonlinear loads [17].

In modern industries, power electronics-based drives such as the current-source-inverter-fed synchronous motor drive, thruster converter-based dc motor drive, VSC-based induction motor drive, etc., are increasingly used whose performance and control largely depend upon the supply voltage quality. Moreover, these nonlinear industrial loads give rise to additional harmonic distortion in the supply voltage at the point of common coupling (PCC) due to the harmonic voltage drop into the feeder impedance, particularly when the feeder impedance is large.

In this paper, a simple generalized control algorithm for the self-supported DVR is developed based on the basic SRFT. This novel algorithm makes use of the fundamental positive sequence phase voltages extracted by sensing only two unbalanced and/or distorted line voltages. The algorithm is general enough to handle linear as well as nonlinear loads. The self supported DVR maintains balanced sinusoidal load voltage with desired magnitude against any supply voltage quality problem even when the load is unbalanced and nonlinear in nature. The algorithm based on instantaneous symmetrical components along with the complex Fourier transform to protect unbalanced and nonlinear load discussed in [17] is computationally demanding and requires huge memory space. The approach discussed here is comparatively simple as it needs only the extraction of the fundamental positive-sequence phase terminal voltages, thus making it computationally simpler with the least memory requirement. The proposed fundamental positive-sequence extractor requires the sensing of only two line voltages of supply. This reduces the analog-to-digital converter (ADC) requirements of a digital controller and corresponding sensing element. Moreover, it is able to extract three fundamental positive-sequence phase voltages irrespective of the distribution system configuration such as three-phase, four-wire or three-phase, three-wire system where the neutral is not available for sensing phase voltages.

In this paper, a hybrid structure of the self-supported DVR is considered in which a shunt capacitor filter is used to provide the low impedance path for higher order harmonics of the load currents [17]. The DVR is realized by three single-phase H-bridge VSCs with a constant switching frequency hysteresis band voltage controller [18]. The proposed control algorithm is validated through extensive\ simulation and real-time experimental studies performed using an OPAL-RT real-time digital simulator and a DSPACE DS1103 digital signal processor.

## **II. DVR CONTROL STRATEGY:**

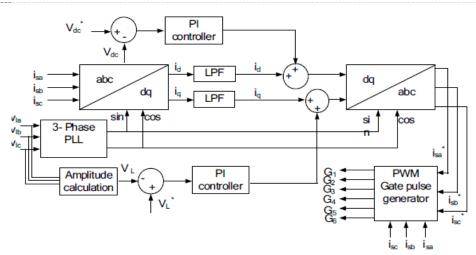

The proposed algorithm is based on the estimation of reference supply currents. It is similar to the algorithm for the control of a shunt compensator like DSTATCOM for the terminal voltage regulation of linear and nonlinear loads [6]. The proposed control algorithm for the control of DVR is depicted in Fig.1.

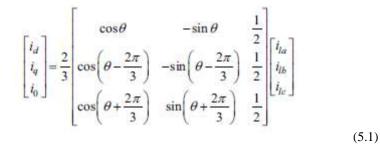

The series compensator known as DVR is used to inject a voltage in series with the terminal voltage. The sag and swell in terminal voltages are compensated by controlling the DVR and the proposed algorithm inherently provides a self-supporting dc bus for the DVR. Three-phase reference supply currents (isa\*, isb\*,isc\*) are derived using the sensed load voltages (vla, vlb, vlc), terminal voltages (vta, vtb, vtc) and dc bus voltage (vdc) of the DVR as feedback signals. The synchronous reference frame theory based method is used to obtain the direct axis (id) and quadrature axis (iq) components of the load current. The load currents in the three-phases are converted into the d-q-0 frame using the Park's transformation as,

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

Fig.1. Control scheme of the DVR

A three-phase PLL (phase locked loop) is used to synchronies these signals with the terminal voltages (vta, vtb, vtc). The d-q components are then passed through low pass filters to extract the dc components of id and iq. The error between the reference dc capacitor voltage and the sensed dc bus voltage of DVR is given to a PI (proportional-integral) controller of which output is considered as the loss component of current and is added to the dc component of id. Similarly, a second PI controller is used to regulate the amplitude of the load voltage (Vt). The amplitude of the load terminal voltage is employed over the reference amplitude and the output of PI controller added with the dc component of iq. The resultant currents are again converted into the reference supply currents using the reverse Park's transformation. Reference supply currents (isa\*, isb\*,isc\*) and the sensed supply currents (isa, isb, isc) are used in PWM current Controller to generate gating pulses for the switches. The PWM controller operates at a frequency of 10 kHz and the gating signals are given to the three-leg VSC for the control of supply currents.

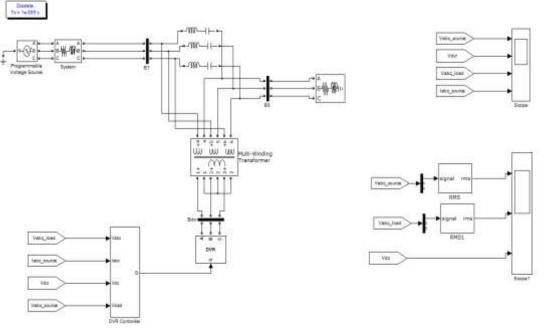

The DVR is modeled and simulated using the MATLAB and its Simulink and Power System Block set (PSB) toolboxes. The MATLAB model of the DVR connected system is shown in Fig.2. The three-phase source is connected to the three-phase load through series impedance and the DVR. The considered load is a lagging power factor load. The VSC of the DVR is connected to the system using an injection transformer.

Fig.2. MATLAB based model of the three-phase DVR connected system

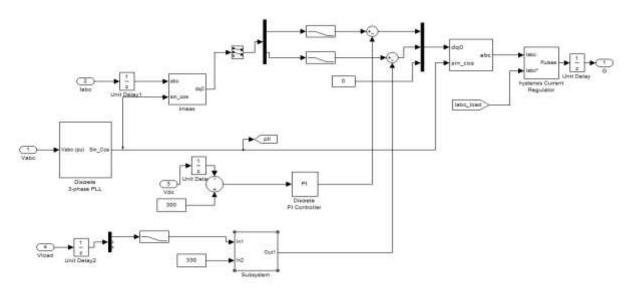

In addition, a ripple filter for filtering the switching ripple in the terminal voltage is connected across in the terminals of the secondary of the transformer. The dc bus capacitor of DVR is selected based on the transient energy requirement and the dc bus voltage is selected based on the injection voltage level. The dc capacitor decides the ripple content in the dc voltage. The proposed control algorithm is modeled in MATLAB as shown in Fig.5.3. The reference supply currents are derived from the sensed load voltages, supply currents and dc bus voltage of DVR. The output of the PI controller used for the control of dc bus voltage of DVR is added with the direct axis component of current. Similarly, the output of the PI controller used for the control of the amplitude of the load voltage is added with the quadrature axis component.

Fig.3. MATLAB based model of the proposed control method

### **III. RESULTS AND DISCUSSION:**

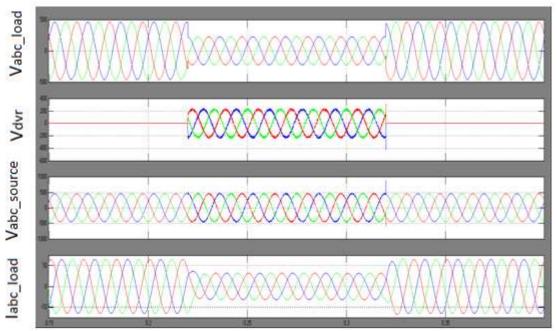

The proposed control scheme of DVR is verified through simulation using MATLAB software along with its Simulink and Power System Block set (PSB) toolboxes. The DVR is tested under different operating conditions like sag (Fig.4) and swell (Fig.5) at the terminal voltages (Vta, Vtb, Vtc). In Fig.4, the terminal

## ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

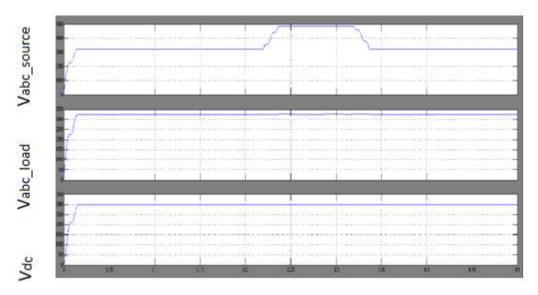

voltage has a sag of 30% with a magnitude at 70% of rated value at 0.22 sec and occurs up to 0.32 sec. The DVR injects fundamental voltage (Vc) in series with the terminal voltages (Vla, Vlb, Vlc). The load voltage is maintained at the rated value. The terminal voltage (Vt), supply current (is), amplitude of terminal voltage (Vt) the amplitude of load voltage (VL) and the dc bus voltage (Vdc) of DVR are also shown in the Fig.4. It is observed that the dc bus voltage of DVR is maintained at reference value.

Fig.4a. Dynamic behavior of DVR for voltage sag compensation

# Time (sec)

Fig.4b. RMS Values of Voltage Sag Compensation

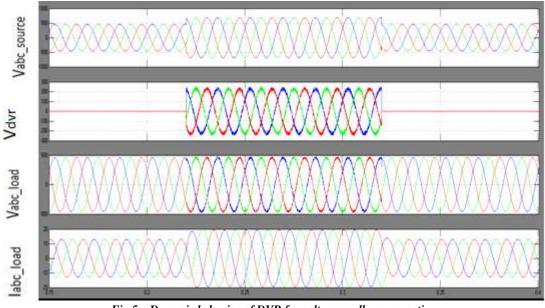

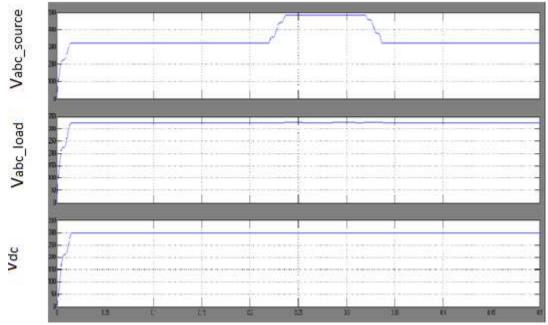

Similarly, in Fig.6.2, a swell in terminal voltage (Vt) has occurred at 0.22 sec up to 0.32 sec and the load voltage (VL) is observed to be satisfactory due to the proper voltage injection by the DVR. The load voltage (VL) is maintained at the rated value. The terminal voltage (Vt) supply current (Is), the amplitude of terminal voltage (Vt), the amplitude of the load voltage (VL) and the dc bus voltage (Vdc) of DVR are also shown in the Fig.5. It is observed that the dc bus voltage of DVR is maintained at reference value, though perturbation is occurring during transients.

Fig.5a. Dynamic behavior of DVR for voltage swell compensation

Fig.5b. RMS Values of Voltage Swell Compensation

## **IV.** CONCLUSION

A new control strategy based on current mode control for Dynamic Voltage Restorer (DVR) has been proposed to mitigate the power quality problems in the terminal voltages. The DVR is controlled indirectly by controlling the supply current. The reference supply currents are estimated using the sensed load terminal voltages and the dc bus voltage of DVR. The control scheme is based on synchronous reference frame theory (SRFT) for the operation of a capacitor supported DVR. The proposed control scheme of DVR has been validated the compensation of sag and swell in terminal voltages. The performance of the DVR has been found very good to mitigate the voltage power quality problems. Moreover, it has been found capable to provide self supported dc bus of the DVR through power transfer from ac line at fundamental frequency.

## V. REFERENCES

- [1] Math H.J. Bollen, Understanding Power Quality Problems- Voltage Sags And Interruptions, IEEE Press, New York, 2000.

- [2] A. Ghosh and G. Ledwich, Power Quality Enhancement using Custom Power devices, Kluwer Academic Publishers, London, 2002.

- [3] Math H. J. Bollen and Irene Gu, Signal Processing of Power Quality Disturbances, Wiley-IEEE Press, 2006.

- [4] R. C. Dugan, M. F. McGranaghan and H. W. Beaty, Electric Power Systems Quality. 2nd Edition, New York, McGraw Hill,2006.

- [5] Antonio Moreno-Munoz, Power Quality: Mitigation Technologies in a Distributed Environment, Springer-Verlag London limited, London 2007.

- [6] K.R. Padiyar, FACTS Controllers in Transmission and Distribution, New Age International, New Delhi, 2007.

- [7] IEEE Recommended Practices and Recommendations for Harmonics Control in Electric Power Systems, IEEE Std. 5 19,1992.

- [8] M. Vilathgamuwa, R. Perera, S. Choi, and K. Tseng, "Control of energy optimized dynamic voltage restorer", in Proc. of IEEE IECON'99, vol. 2,1999, pp. 873–878.

- [9] B. N. Singh, A. Chandra, K. Al-Haddad and B. Singh, "Performance of sliding-mode and fuzzy controllers for a static synchronous series compensator", IEE Proc. on Generation, Transmission and Distribution, vol. 146, no. 2, pp. 200 – 206, March 1999.

- [10] Il-Yop Chung., Dong-Jun Won, Sang-Young Park, Seung-Il Moon and Jong-Keun Park, "The DC link energy control method in dynamic voltage restorer system", International Journal of Electrical Power & Energy Systems, vol. 25, no. 7, pp. 525-531, Sept. 2003.

- [11] A. Ghosh, A.K Jindal and A Joshi, "Design of a capacitorsupported dynamic voltage restorer (DVR) for unbalanced and distorted loads", IEEE Trans. on Power Delivery, vol. 19, no.1, pp. 405 – 413, Jan. 2004.

- [12] A. Moreno-Munoz, D Oterino, M Gonzalez, F A Olivencia and J.J. Gonzalez-de-la-Rosa, "Study of sag compensation with DVR", in Proc. of IEEE MELECON, Benalmadena (Malaga Spain, May 2006, pp 990-993.

- [13] Amit Kumar Jindal, Arindam Ghosh and Avinash Joshi, "Critical load bus voltage control using DVR under system frequency variation," Electric Power Systems Research, 2007, doi: 10.1016/j.epsr. 2007.02.006.

#### **CITE AN ARTICLE**

Dora, H. M., & Vikas, M. (2018). COMPARATIVE CONTROL OF DVR FOR POWER QUALITY IMPROVEMENT UNDER UNBALANCED VOLTAGE SAG. *INTERNATIONAL JOURNAL OF* ENGINEERING SCIENCES & RESEARCH TECHNOLOGY, 7(6), 275-281